产品特性介绍

产品选型表

| 器件型号 | PG2L25H | PG2L50H | PG2L50M | PG2L100H | PG2L100HX1 | PG2L200H | ||

| 逻辑资源 | 逻辑单元 | 26700 | 53700 | 44700 | 99900 | 99900 | 239700 | |

| LUTs | 17800 | 35800 | 29800 | 66600 | 66600 | 159800 | ||

| Flip-Flops(个) | 35600 | 71600 | 59600 | 133200 | 133200 | 319600 | ||

| RAM资源 | 分布式RAM(Kbit) | 344 | 594 | 525 | 1244 | 1244 | 2469 | |

| 块RAM数量(36Kbit/块) | 55 | 85 | 88 | 155 | 155 | 415 | ||

| 块RAM(Kbit) | 1980 | 3060 | 3168 | 5580 | 5580 | 14940 | ||

| 时钟资源 | GPLL+PPLL+FPLL | 3+3+0 | 5+5+0 | 2+2+2 | 6+6+0 | 6+6+0 | 10+10+0 | |

| IO资源 | 最大用户IO | 150 | 250 | 146 | 300 | 300 | 500 | |

| 最大差分IO(对) | 72 | 120 | 71 | 144 | 144 | 240 | ||

| DDR3(Mbps) | 1066 | 1066 | \ | 1066 | 1066 | 1066 | ||

| DDR4(Mbps) | \ | \ | 1866 | \ | \ | \ | ||

| 硬核资源 | APM(25*18) | 80 | 120 | 120 | 240 | 240 | 740 | |

| ADC硬核 | 1 | 1 | 1 | 1 | 1 | 1 | ||

| PCIe Gen2x4 | 1 | 1 | \ | 1 | 1 | 1 | ||

| AES模块 | 1 | 1 | 1 | 1 | 1 | 1 | ||

| HSST(6.6Gbps/lane) | 4 | 4 | \ | 8 | 8 | 16 | ||

| MIPI D-PHY硬核(2.5Gbps/lane) | \ | \ | 2 | \ | \ | \ | ||

| 封装 | 尺寸(mm) | 间距(mm) | 用户IO/HSST | |||||

| MBG256 | 14 x 14 | 0.8 | 146/0 | |||||

| MBG324 | 15 x 15 | 0.8 | 210/0 | 210/0 | 210/0 | |||

| MBG325 | 15 x 15 | 0.8 | 150/4 | |||||

| FBG4842 | 23 x 23 | 1 | 250/4 | 285/4 | 285/4 | |||

| FBB4842 | 23 x 23 | 1 | 285/4 | |||||

| FBG6763 | 27 x 27 | 1 | 300/8 | 300/8 | ||||

| FBB6763 | 27 x 27 | 1 | 400/8 | |||||

| FFBG1156 | 35 x 35 | 1 | 500/16 | |||||

| 备注: 1、PG2L100HX支持1.25Gbps高速LVDS 2、FBG484和FBB484管脚兼容 3、FBG676和FBB676管脚兼容 |

||||||||

技术文档

-

PK04009_PG2L200H-FBB484_V1.0

PK04009_PG2L200H-FBB484_V1.0 2023.12.11

2023.12.11

-

PK04008_PG2L200H-FBB676_V1.0

PK04008_PG2L200H-FBB676_V1.0 2023.12.11

2023.12.11

-

PK04007_PG2L200H-FFBG1156_V1.0

PK04007_PG2L200H-FFBG1156_V1.0 2023.12.11

2023.12.11

-

PK04006_PG2L50H_MBG324_v1.1

PK04006_PG2L50H_MBG324_v1.1 2023.12.11

2023.12.11

-

PK04005_PG2L50H_FBG484_v1.1

PK04005_PG2L50H_FBG484_v1.1 2023.12.11

2023.12.11

-

PK04004_PG2L25H_MBG325_v1.1

PK04004_PG2L25H_MBG325_v1.1 2023.12.11

2023.12.11

-

PK04003_PG2L100H_FBG484_V1.2

PK04003_PG2L100H_FBG484_V1.2 2023.12.11

2023.12.11

-

PK04002_PG2L100H_MBG324_V1.3

PK04002_PG2L100H_MBG324_V1.3 2023.12.11

2023.12.11

-

PK04001_PG2L100H_FBG676_V1.3

PK04001_PG2L100H_FBG676_V1.3 2023.12.11

2023.12.11

-

UG040012_Logos2系列单板硬件设计用户指南_V1.4

UG040012_Logos2系列单板硬件设计用户指南_V1.4 2023.12.11

2023.12.11

-

UG040010_Logos2系列产品低功耗设计用户指南

UG040010_Logos2系列产品低功耗设计用户指南 2023.12.11

2023.12.11

-

UG040009_Logos2系列FPGA模数转换模块(ADC)用户指南_V1.6

UG040009_Logos2系列FPGA模数转换模块(ADC)用户指南_V1.6 2023.12.11

2023.12.11

-

UG040007_Logos2系列产品GTP用户指南_V1.2

UG040007_Logos2系列产品GTP用户指南_V1.2 2023.12.11

2023.12.11

-

UG040006_Logos2系列FPGA输入输出接口(IO)用户指南_V1.2

UG040006_Logos2系列FPGA输入输出接口(IO)用户指南_V1.2 2023.12.11

2023.12.11

-

UG040005_Logos2系列FPGA配置(configuration)用户指南_V1.3

UG040005_Logos2系列FPGA配置(configuration)用户指南_V1.3 2023.12.11

2023.12.11

-

UG040004_Logos2系列FPGA时钟资源(Clock)用户指南_V1.2

UG040004_Logos2系列FPGA时钟资源(Clock)用户指南_V1.2 2023.12.11

2023.12.11

-

UG040003_Logos2系列FPGA算术处理模块(APM)用户指南_V1.3

UG040003_Logos2系列FPGA算术处理模块(APM)用户指南_V1.3 2023.12.11

2023.12.11

-

UG040002_Logos2系列FPGA专用RAM模块(DRM)用户指南_V1.1

UG040002_Logos2系列FPGA专用RAM模块(DRM)用户指南_V1.1 2023.12.11

2023.12.11

-

UG040001_Logos2系列FPGA可配置逻辑模块(CLM)用户指南_V1.4

UG040001_Logos2系列FPGA可配置逻辑模块(CLM)用户指南_V1.4 2023.12.11

2023.12.11

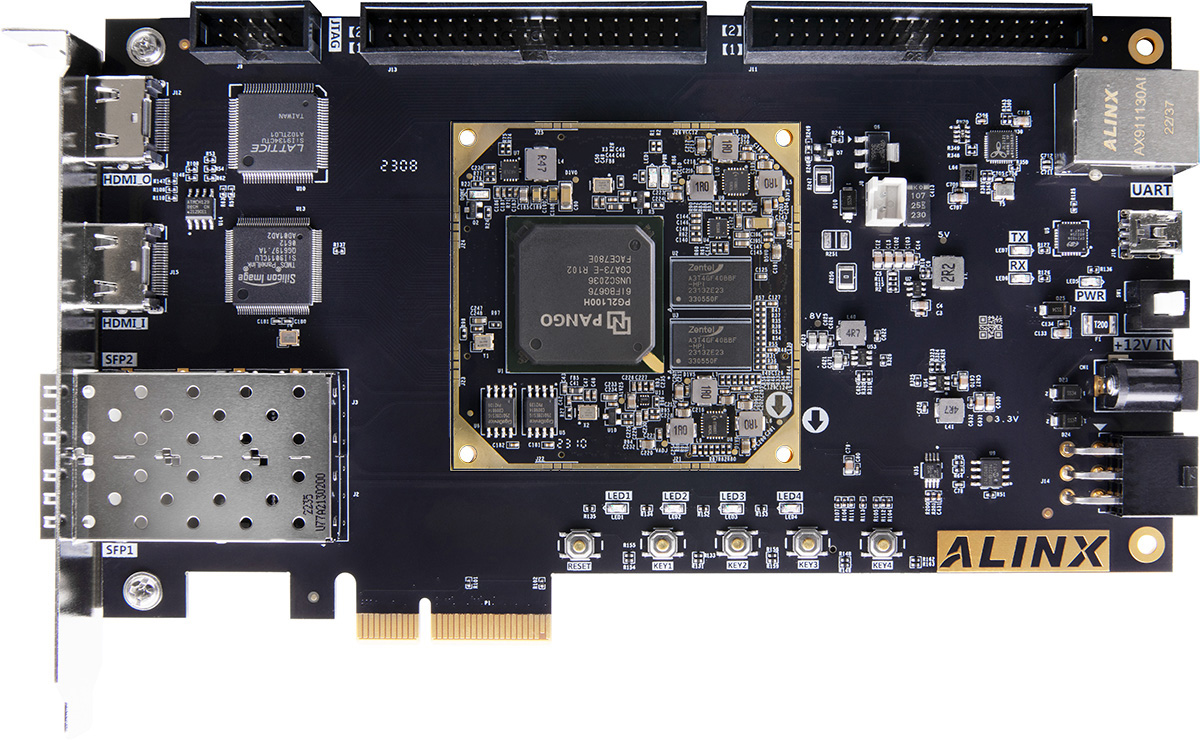

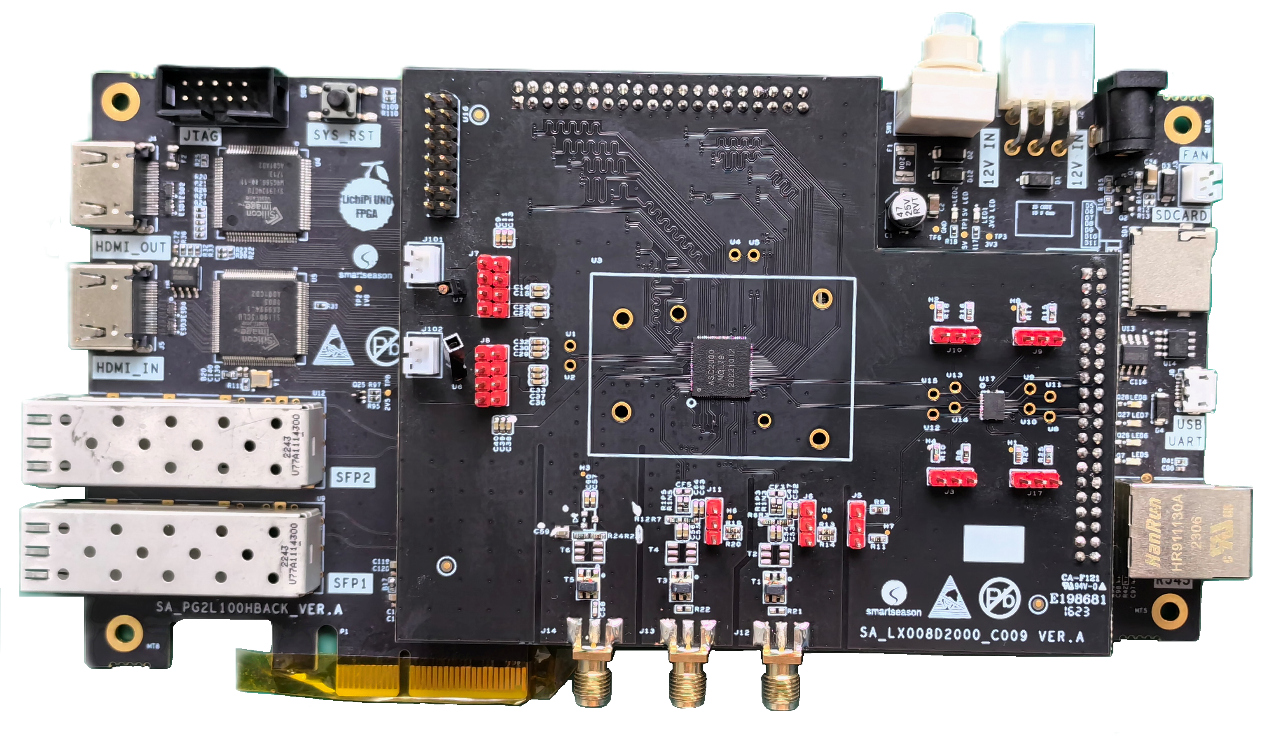

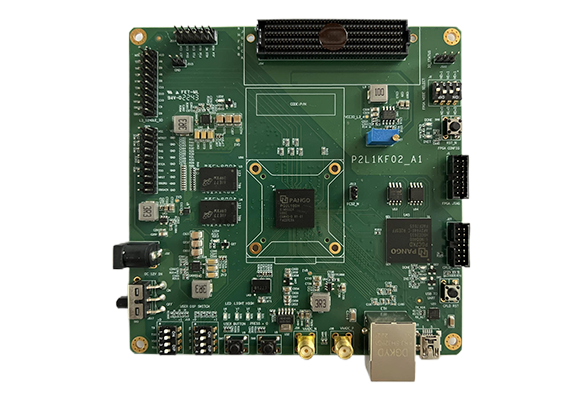

开发板及套件